Sonntag, 30. Januar 2011

Neuer Aufbau

Ich kann einen Teilerfolg vermelden. Die UART-Platine hat (mehr oder weniger) funktioniert. Ich habe ein Programm geschrieben, welches über die serielle Schnittstelle empfangene Zeichen als Echo zurücksendet. Hat wunderbar funktioniert. Die ersten paar Minuten. Doch dann sind seltsame Probleme aufgetreten, und der UART hat keinen Mucks mehr von sich gegeben. Beim Messen mit dem Oszilloskop habe ich dann blöderweise nen Kurzschluss auf dem UART-Board verursacht, das hat die Isolation der 5V-Leitung beschädigt und evtl. noch andere Leitungen. Da ich mit dem Aufbau sowieso unzufrieden bin, (u.A. weil sich schlecht messen lässt), werde ich mir eine Platine fertigen lassen. Dann bin ich auch meine Drahtigel los. Mal sehen, ob ich das Layout dafür in der kommenden Woche fertig bekomme.

Sonntag, 23. Januar 2011

IO Select

Zur Erzeugung der Chip Selects der Peripherie muss ebenfalls ein Adressdecoder her. Dafür bietet sich der 74HC138 an, ein 3-8 Multiplexer mit invertierenden Ausgängen. Auf sehr einfache Weise lassen sich so Chip Selects für 8 verschiedene Geräte erzeugen, die jeweils 32 Byte Adressraum zur Verfügung haben. Den UART lege ich einfachheitshalber auf IO-Adresse 0x00.

Die Verdrahtung ist einfach:

|

| IO-Decoder |

Der 16C550 lässt sich direkt an den Bus anschließen. Die meisten Bussignale liegen als low- und high-active vor. Die Interruptleitung ist high-active.

Mittwoch, 19. Januar 2011

Serial Board

Als nächstes kommt die serielle Schnittstellenkarte dran. Ich habe einen Z80-SIO und einen 16C550. Der Z80-SIO ist jener Baustein, der früher typischerweise in Verbindung mit einer Z80-CPU für RS232 benutzt wurde. Der 16C550 ist ebenfalls schon älter, wird aber heute noch auf seriellen Erweiterungskarten für den PC verbaut.

Ich kenne beide Chips nicht. Die Datenblätter sind beide ziemlich komplex, ich bin noch unendschieden, welchen der beiden ich verwenden werde.

Der SIO wurde ja zur Verwendung mit dem Z80 designt, aber es gibt nicht allzu viel Infos dazu im Netz. Zum 16C550 findet man deutlich mehr, und er ist nicht ganz so komplex.

Erster Erfolg!

Endlich hab ich den Z80 dazu bewegt, das zu tun was ich sage!! :-) Das Testprogramm ist erfolgreich gelaufen.

Die bidirektionalen Bustreiber (74HC245) der RAM-Karte und der CPU-Karte haben manchmal gegeneinander getrieben. Das hätte ich gar nicht richtig gemerkt, da das nur im Memory-Refresh-Zyklus geschehen ist. Das Symptom war dabei, dass sich der dsPIC resettet hat. Gut, dass die Bustreiber kurzschlussfest zu sein scheinen, jedenfalls ist keiner kaputt gegangen... Ach ja, Empfehlung: Datenblätter ganz genau lesen, das erspart viel Frustration und abkotzen!!

Ich poste hier schon mal die Schematics der beiden Boards:

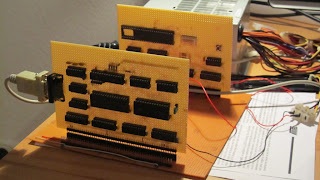

Und in Natura sieht das jetzt so aus:

Die bidirektionalen Bustreiber (74HC245) der RAM-Karte und der CPU-Karte haben manchmal gegeneinander getrieben. Das hätte ich gar nicht richtig gemerkt, da das nur im Memory-Refresh-Zyklus geschehen ist. Das Symptom war dabei, dass sich der dsPIC resettet hat. Gut, dass die Bustreiber kurzschlussfest zu sein scheinen, jedenfalls ist keiner kaputt gegangen... Ach ja, Empfehlung: Datenblätter ganz genau lesen, das erspart viel Frustration und abkotzen!!

Ich poste hier schon mal die Schematics der beiden Boards:

|

| RAM-Board |

|

| CPU-Board |

|

| CPU-Board Rückseite |

|

| RAM-Board |

|

| Gesamter Aufbau |

Mit diesem Aufbau kann man bisher noch nicht so viel anfangen:

Ein dsPIC ist über die serielle Schnittstelle mit meinem PC verbunden. Über Terminal kann ich nun dem PIC sagen, die Bustreiber der RAM-Karte hochohmig zu schalten. So kann dann das EEPROM und den RAM gelesen und beschrieben werden, ohne mit der CPU in Konflikt zu geraten.

Ansonsten "lebt" die CPU in ihrem eigenen Mikrokosmos und hat keinen Kontakt zu Aussenwelt, was das Ganze noch etwas nutzlos erscheinen lässt ;-)

Das wird sich aber bald ändern, denn als nächstes ist eine serielle Karte geplant, mit der die Kommunikation zwischen dem Z80 und einem PC möglich wird.

Ansonsten "lebt" die CPU in ihrem eigenen Mikrokosmos und hat keinen Kontakt zu Aussenwelt, was das Ganze noch etwas nutzlos erscheinen lässt ;-)

Das wird sich aber bald ändern, denn als nächstes ist eine serielle Karte geplant, mit der die Kommunikation zwischen dem Z80 und einem PC möglich wird.

Dienstag, 18. Januar 2011

Erstes Testprogramm

Wenn die beiden Boards fertig sind und (hoffentlich!) auch noch funzen, muss der Z80 ja auch was zum Ausführen bekommen. Ich habe leider nur etwas Ahnung von Assembler, da muss ich mich noch reinfuchsen. Aber als Erstes werde ich wohl folgendes Programm in den ROM schreiben:

(1) LD A,37

(2) LD (9509), A

(3) HALT

Zeile (1) lädt die Zahl 37 in den Akku. Zeile (2) schreibt den Akkuinhalt an Speicheradresse 9509. Und Zeile (3) hält den Prozessor an.

Das als Opcodes sieht dann folgendermaßen aus:

Addr Codes

0x00 3E 25

0x02 32 25 25

0x05 76

Wenn alles geklappt hat, sollte dann an Position 9509 des RAMs die Zahl 37 stehen.

(1) LD A,37

(2) LD (9509), A

(3) HALT

Zeile (1) lädt die Zahl 37 in den Akku. Zeile (2) schreibt den Akkuinhalt an Speicheradresse 9509. Und Zeile (3) hält den Prozessor an.

Das als Opcodes sieht dann folgendermaßen aus:

Addr Codes

0x00 3E 25

0x02 32 25 25

0x05 76

Wenn alles geklappt hat, sollte dann an Position 9509 des RAMs die Zahl 37 stehen.

Resetschaltung

Die Resetschaltung der CPU ist sehr wichtig, wie ich feststellen musste. Denn das Resetsignal muss ein paar CPU-Takte lang sein, damit der Reset wirklich vollständig durchgeführt wird. Folgende Schaltung verwende ich für den CPU-Reset:

Der Schalter zieht bei Druck !RESET sofort auf Masse. Lässt man den Schalter los, so lädt sich der Kondensator "langsam" wieder auf 5V auf. Der Schmitt-Trigger sorgt mit seiner Hysterese für ein ständig gültiges TTL-Signal. Eine Tastenentprellung bekommt man auch gleich mitgeliefert.

Der Schalter zieht bei Druck !RESET sofort auf Masse. Lässt man den Schalter los, so lädt sich der Kondensator "langsam" wieder auf 5V auf. Der Schmitt-Trigger sorgt mit seiner Hysterese für ein ständig gültiges TTL-Signal. Eine Tastenentprellung bekommt man auch gleich mitgeliefert.

Montag, 17. Januar 2011

Memory Management

Beim Z80 sind die Adressräume für Speicher und externer Peripherie getrennt. Dies vereinfacht das Memory Management etwas, da beim Speicher nur noch entschieden werden muss, ob EEPROM oder RAM angesprochen werden soll.

Nun hat das EEPROM 8192 Byte Speicherkapazität und soll an den Anfang des Adressraums "gemapt" werden. Adressen von 0..8191 sprechen also das EEPROM an, 8192-65535 adressieren den RAM.

Mit folgender Schaltung wird das Chip Select generiert:

Auf Pin 2-3 wird ein Jumper gesteckt. Das Signal !MREQ ist low active und signalisiert einen "Memory Request". Sind die Adressleitungen A13, A14, A15 und !MREQ low, so wird !ROM_CS runter gezogen, welches an !CS des EEPROMS angeschlossen ist. Ist eine der Adressleitungen high, so wird !RAM_CS runter gezogen und so der RAM selektiert.

Das EEPROM:

A16 ist auf GND gelegt. Später werde ich evtl. dies um eine Banken-Logik erweitern, um mehr Speicher ansprechen zu können. Dazu muss ich mir aber erst noch ein paar Gedanken machen, wie das funktionieren könnte.

Nun hat das EEPROM 8192 Byte Speicherkapazität und soll an den Anfang des Adressraums "gemapt" werden. Adressen von 0..8191 sprechen also das EEPROM an, 8192-65535 adressieren den RAM.

Mit folgender Schaltung wird das Chip Select generiert:

|

| Simple Z80-MMU |

Das EEPROM:

Und der RAM:

Sonntag, 16. Januar 2011

Z80 Computer

Der Z80 ist ein 8-Bit Prozessor aus dem Jahre 1976. Verwendet wird/wurde er z.B. im Nintendo Gameboy, TI-Taschenrechnern und vielen Arcade-Game-Automaten. Er ist leistungsmäßig verlgeichbar mit dem 6502, der in C64 Computern zu finden ist.

Mein Ziel ist es, einen kleinen funktionsfähigen Computer um diese CPU herum zu bauen. Ich habe mir diesen Prozessor ausgesucht, weil der Chip noch gut für einen Hobbybastler zu "handlen" ist, und auch der Verdrahtungsaufwand - im Gegensatz zu moderneren Chips - relativ gering ist. Die Z80-CPU besitzt einen 8-Bit Datenbus und einen 16-Bit Adressbus. Es können also bis maximal 64kB RAM direkt adressiert werden. In meinem ersten Design soll er mit 1 MHz betrieben werden.

Und dies ist das Pinout des guten Stücks:

Das Ganze werde ich auf Lochrasterplatinen aufbauen und mit Kupferlackdraht verdrahten.

|

| Z80 im 40 Pin DIP-Gehäuse |

Mein Ziel ist es, einen kleinen funktionsfähigen Computer um diese CPU herum zu bauen. Ich habe mir diesen Prozessor ausgesucht, weil der Chip noch gut für einen Hobbybastler zu "handlen" ist, und auch der Verdrahtungsaufwand - im Gegensatz zu moderneren Chips - relativ gering ist. Die Z80-CPU besitzt einen 8-Bit Datenbus und einen 16-Bit Adressbus. Es können also bis maximal 64kB RAM direkt adressiert werden. In meinem ersten Design soll er mit 1 MHz betrieben werden.

Und dies ist das Pinout des guten Stücks:

Die Ax-Leitungen sind die Adressleitungen, Dx sind die Datenleitungen. An die Phi-Leitung wird der CPU-Takt angelegt.

Für ein Minimalsystem muss ROM und RAM angeschlossen werden. Das ROM enthält den "Bootstrap"-Code, um den Rechner zu starten. In diesem Projekt wird es wohl gleich das ganze Betriebssystem sein :-)

In den RAM können dann weitere Programme aus externen Quellen nachgeladen werden und er wird als Arbeitsspeicher benutzt.

Wird die CPU neu gestartet, liest sie vom Byte an Adresse 0 (dem ersten Byte des Speichers, in diesem Projekt liegt es im EEPROM) an den Speicher aus. Das "Betriebssystem" muss also gleich am Anfang des Speichers liegen. Wie kommt es dort hin? Dafür werde ich einen Mikrocontroller vorsehen, der über eine serielle Schnittstelle mit einem PC verbunden ist. Auf dem PC wird man so die Software entwickeln und kompilieren können, um sie dann in den EEPROM zu schreiben. Der µC wird ebenfalls den RAM lesen und schreiben können. So werde ich dann auch anfangs die Funktion der CPU prüfen können, da sie ja noch keine Schnittstelle zur Aussenwelt hat.

Ich teile das Projekt für den Anfang erstmal auf zwei Karten auf: Die Prozessorkarte, auf der die CPU, der 1MHz-Quarz und Bustreiber sitzen. Auf der anderen wiederum Bustreiber, EEPROM, RAM und der Controller.

Folgende Bauteile habe ich ausgewählt:

- Zilog Z80 CPU 4MHz

- 1 MHz Quarz

- Invertierender Schmitt-Trigger 74HC14

- Bustreiber 74HC244, 74HC245

- Controller dsPIC30F4012

- 8kB EEPROM Atmel 28c64

- 128kB RAM 628128

- NAND 74LS00

- OR 74LS32

...sowie natürlich die obligatorischen 100nF an jedem IC.

Das Ganze werde ich auf Lochrasterplatinen aufbauen und mit Kupferlackdraht verdrahten.

Samstag, 15. Januar 2011

Abonnieren

Posts (Atom)